CPU Architecture

The Von Neumann Architecture

What is a CPU? It’s the brain of a computing system, carrying out instructions one after another. The way the CPU is designed and executes instructions is known as the Von Neumann architecture.

It describes a system where instructions are stored in memory and the CPU follows them- one instruction at a time. Let me show you how it works, by looking at the components inside a CPU.

We’ll start with the Arithmetic & Logic Unit. This basically does all the calculations- additions, subtractions, multiplications, divisions, greater than less than comparisons, and logical operations. It stores the intermediate results of calculations in the Accumulator register. A register is a CPU component that temporarily holds tiny pieces of data, and are super quick to read/write to- way quicker than any other form of memory. So in the case of the accumulator, the ALU may want to add a number to the result of a previous calculation, and would require instant access to that previous total.

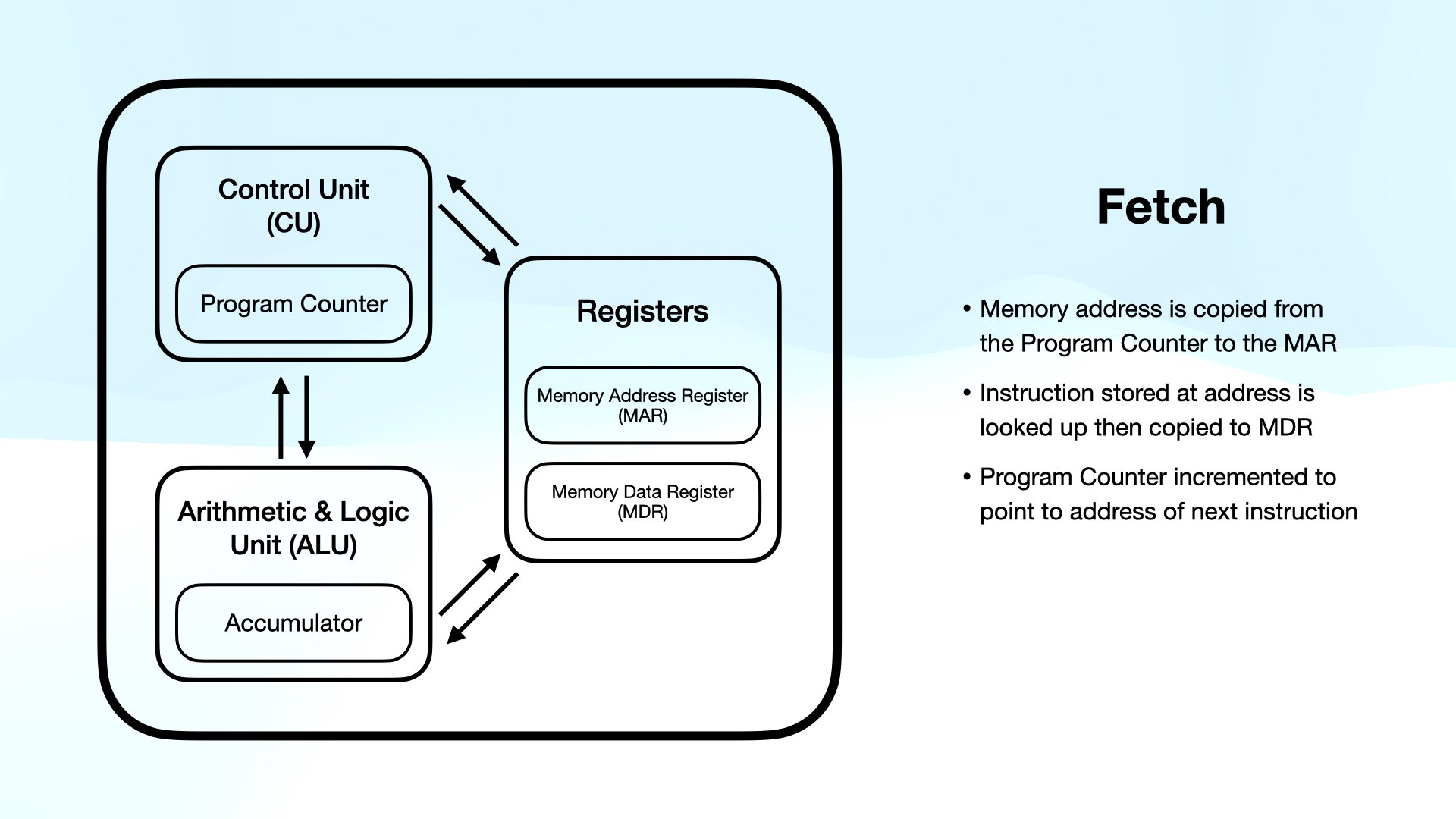

Let me introduce you to 2 other registers. The Memory Address Register holds any memory address about to be used by the CPU. The Memory Data Register holds the actual data or instruction fetched from memory, or waiting to be written to memory.

This is all governed by the control unit, controlling the flow of data inside the CPU, for example to registers, and outside the CPU, for example to main memory. It also contains the Program Counter register, which holds the memory address of the instruction for each cycle.

The Fetch-Execute-Decode Cycle

At the fetch stage of the cycle, the memory address is copied from the Program Counter to the Memory Address Register.The instruction stored at the address is looked up, then copied to the Memory Data Register. And finally, the Program Counter is incremented to point to the address of the next instruction, ready for the next cycle.

At the decode stage, the instruction is decoded by the Control Unit. And at the execute stage, the instruction is carried out by the Control Unit. Whether that’s loading data from memory, writing data to memory, performing a calculation, changing the address in the Program Counter, or halting the program.

CPU Cache

The last CPU component I want to talk about, is the cache. The cache is a type of very expensive but very fast memory- it’s slower than registers, but faster than RAM. It stores data and instructions that are most often used for the processor to access them quickly. When the CPU requests data, it’ll check the cache to see if it’s there first. It’s also of low capacity, but this varies depending on the level of cache. L1 is the quickest, but has the lowest capacity. L2 is slower, but can hold more. And then L3 is even slower, but can hold even more.

Summary

The Von Neumann architecture is the design and execution of instructions for a CPU, which consists of an Arithmetic & Logic Unit, Accumulator register, Memory Address Register, Memory Data Register, Control Unit, Program Counter register, and Cache.

The Fetch-Execute-Decode cycle is the process of the CPU retrieving instructions from memory, decoding them, and executing them.

The Cache is a type of fast memory that stores data and instructions that are most often used by the processor.